# **Analysis of New bridge 9-level Inverter**

Harpreet Bedi, Rk Sharma SEEE, Lovely Professional university, India E-mail: - harpreet.17377@lpu.co.in

#### Abstract

Recently presented topologies accomplish a greater number of yield voltage with a smaller count of semiconductors tools, dc signals. Lessening of switches and DC signals declines the prize, features, many-sided quality and upgrades general execution. Improved topology can deliver more levels of yield voltage with 7 switches as it were. Also, huge lessening in voltage worry over the switches can be accomplished. A near investigation of upgraded topology with the traditional topology and as of late distributed topologies has been made as far as different switches, control diodes, circuit prerequisite, DC voltage signals and other voltage. Multi-bearer beat width tweak technique is embraced for creating the exchanging beats. Recreation investigation of the improved topology has been completed utilizing Matlab/Simulink

Keywords: Inverters, cascaded multilevel inverters, power electronics-bridge inverters

### 1. Introduction

Requirement of higher power for different industry-oriented applications is being increasing these days.to supplement the requirement of high power many structures and algorithms have been proposed. The main reason for writing this paper is to boost the standard of the production and decrease the amount of shifting apparatus and dc signals. Multilevel inverters are developing their leads to meet high and increased high power with increased harmonic performance, quality output i.e. equal to sine -wave and eliminates electro-magnetic barrier i.e. imaginable with the help of dissimilar de-levels that are intended on the output voltage signal. Some of the recent applications of electrical engineer requires more power and more voltage that cannot be availed with semiconductor switches intentionally for the different devices. To solve these faults and issues, different applications which requires more power and voltage were developed multilevel converters.

Recently, multilevel inverters are being the main and crucial inverters which intend to use power applications for examples current motor Drive AC transmission devices (FACTS), electrical vehicles, drives systems etc. The other main concern of this inverter is to use the devices in alignment and checking the outcomes to decrease the voltage on every step and with the usage of less dc voltage to increase the input level of voltage. In multilevel inverters we are using batteries, capacitors power electronic devices and other DC sources. The power rating of every device depends on the voltage source which is used in these inverters. There are different types of inverter topologies which are used in recent times are: -

Clamped diode: This inverter uses power electronic devices for the operation to fluctuate the capacitor voltage into DC Voltage. The main idea of this technology was to maintain a different distance from overcharging of capacitors.

Multilevel Capacitor: The elaborated method for reversal is that in this method the capacitors should be pre charged and to some extent like diode braced strategy. Folding is done through capacitors against the diodes and sometimes that phenomenon is called as imbricated cell multilevel inverter

### Series H-Bridge:

Using this type of inverters, we can increase the voltage level up to 3 times and circuitry is composed of diodes and switches and is most commonly used inverter and often uses dc sources. In order to overcome distortions, we can change the style of inverters.

#### 2 Basic Circuit of inverter

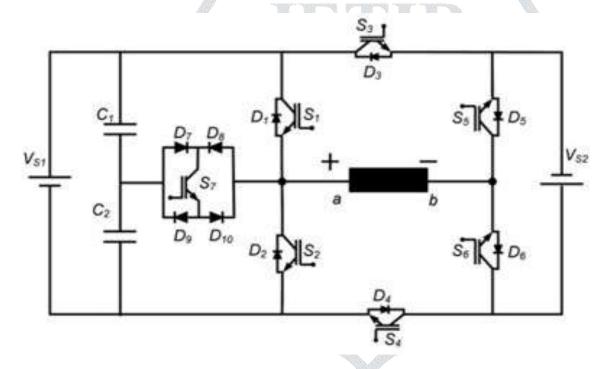

The building block of inverter is exhibited in the figure. 2 voltages with two capacitors are used in the circuit. The capacitors voltages are Vdc/2 and Vdc/2 each and comprises of 7 switches and 4 diodes.

Fig. 1 Nine level inverter

We will find that when two sources are equal then we can claim it as an as regular inverter otherwise irregular inverter. By varying the signal levels of individuals levels, we can obtain output voltage signals. When these voltage signals are equal the output voltage will be 9 levels. The methods of obtain 9 level inverter is:-In this method we obtain the voltage signal at different voltage levels keeping the source voltage equal and circuits are designed with voltage level twice, thrice than the input level.

# Different Switching Combinations

| S.no | voltage<br>levels | switch                                           | Diodes                |  |

|------|-------------------|--------------------------------------------------|-----------------------|--|

| 1    | 1                 | S4, S7                                           | D6, D7, D1            |  |

| 2    | 2                 | S4, S5                                           | D <sub>2</sub>        |  |

| 3    | 3                 | S4, S5, S7                                       | D7, D10               |  |

| 4    | 4                 | S1, S4, S5                                       | -                     |  |

| 5    | 0                 | -                                                | -                     |  |

| 6    | -1                | S3, S7                                           | D5, D8, D9            |  |

| 7    | -2                | S <sub>3</sub> , S <sub>6</sub>                  | <b>D</b> <sub>7</sub> |  |

| 8    | -3                | S3, S6, S7                                       | D8, D9                |  |

| 9    | -4                | S <sub>2</sub> , S <sub>3</sub> , S <sub>6</sub> | -                     |  |

Table 2. When source voltage is same

| S.No. | Voltage levels | If<br>VS1=VS2=2V | Output<br>voltage |

|-------|----------------|------------------|-------------------|

| 1     | 2V             | 2*2              | 4V                |

| 2     | 3V/2           | (3*2)/2 = 6/2    | 3V                |

| 3     | v              | 2                | 2V                |

| 4     | V/2            | 2/2              | 1V                |

| 5     | 0              | 0                | 0                 |

| 6     | -V/2           | -2/2             | -1V               |

| 7     | -V             | -2               | -2V               |

| 8     | -3V/2          | -(3*2)/2 = 6/2   | -3V               |

| 9     | -2V            | -2*2             | -4V               |

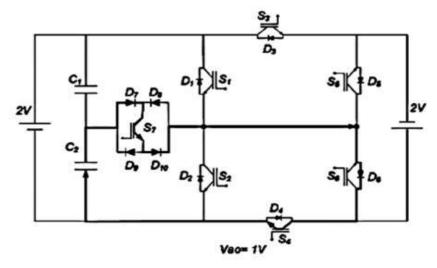

# When output level is one volt

Fig. 2 When output level is one volt

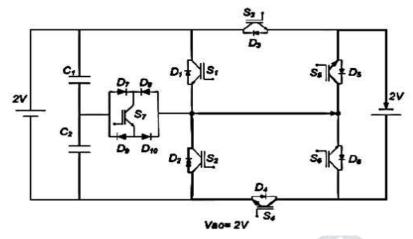

# When output level is two volt

When the voltage is twice, when voltage is twice and at the times switching of diode plays an important role and 3 diodes are conducting.

Fig. 3 When output level is two volts

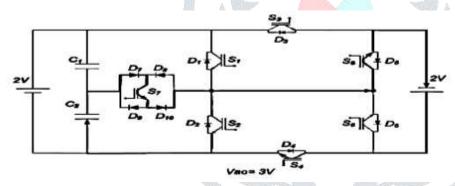

## When output level is three volts

Output voltage will be thrice with three switching combinations which are shown. Different diodes are capacitors will be required to maintain the voltage at thrice level and only 2 diodes are operational.

Fig. 4 When output level is three volts

In this paper we have checked for output voltage for different levels from positive to negative values and obtain that various switching combinations will require the output voltage and for the sane different combinations of capacitors and diode will be used to shift the voltage at the desire levels.

### 3. Result

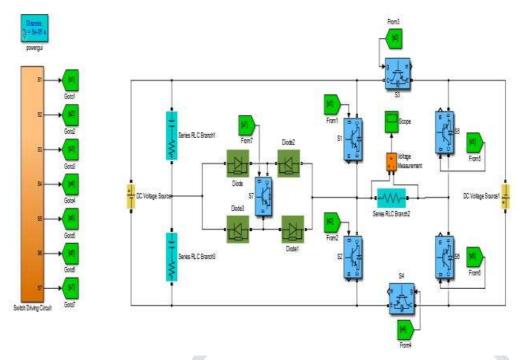

The Diagram elaborates that 9-level inverter model with 2 DC sources and 2 capacitors which are supposed to be charged to voltage half level. Inverter is using 2 sources as DC with 50v each. The IGBT are basically diodes and have internal resistor value of 1m  $\Omega$ .

Fig. 5. enhanced multi-level inverter

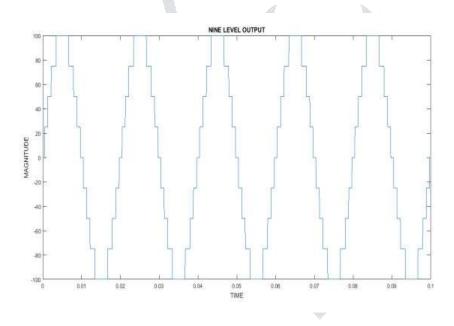

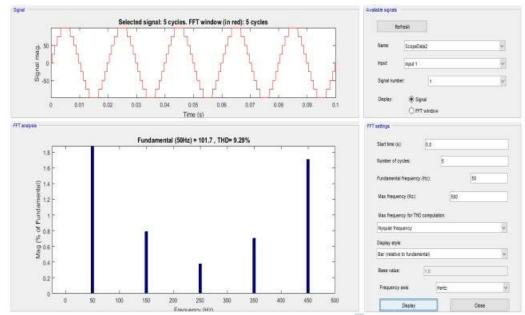

Figure 6 above shows the inverter waveform and harmonic distortion spectrum in next figure.101.7V is peak output value and load resistive is 100ohms and with this settings and values both the current and voltages are having same shapes and output voltage obtained is above 9 volts which justify our title of the paper.

Fig. 7. Output voltage of inverter

### 4. Conclusion

The main Test is the voltage changing and steady state which will be done in diode clamped and clamped inverter. Series combination of h bridge inverters are using high voltage and high-power drives due to involvement factor with a smaller number of distortion and a smaller number of components in this paper h level bridge inverter was enhanced using several 7 semiconductor switches, 10 diodes, capacitors and 2 sources who are gendering 9 levels of output voltage form power supply source. The inverter designed increase the voltage level up to 9 times with a smaller number of switches, driver circuits, and diodes and can control quality of output bring certain changes at output level and also changes in desired output waveforms.

### References

- S. Lai and F.Z. Peng, "Multilevel converters -a new breed of power converters," IEEE Trans. Ind Appl., vol. 32, no. 3, pp. 50917,M ay/June 1996.

- E. Babaei and S.H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," Elsevier Journal of Energy Conversion and Management, vol. 50, no. II, pp. 27612767,N ov. 2009.

- Ned mohan, Tore.M, undeland, and William.P. Robbins "power electronics, converters, Applications and Design", Third edition, New Delhi, Wiley India

- (P.)Ltd. Reprint. M.H.Rashid "Power electronics: Circuits, Devices and applications. Third edition, Prentice hall, 2004.

- Varsha Singh, member IEEE Electrical Engineering Dept. National institute of Technology, Raipur Raipur, India.S Gupta, S Pattnaik ,Revendra K. Dewangan Electrical Engineering Dept. National institute of Technology, Raipur Raipur, India" New Hybrid Cascade Multilevel Inverter with Less Number of Switches" IEEE 978-1-4799-6042-2/14/2014

- 6. A new N-level high voltage inversion system" Young-Seok Kim, Beom-Seok Seo and Dong-Seok Hyun Dept. of Electrical Engineering, Hanyang Univ., Seongdong-ku, Seoul, 133-791Korea. 1EEE 0-7803-0891-3/1993.

- 7. Harmonics Reduction of Three Phase Five-Level Neutral-Point-Clamped Multilevel Inverter"Nashiren Farzilah Mailah, Sh. Sakinah Tuan Othman, Ishak Aris, M. Norhisam, M.Z.A. Abdul Kadir Department of Electrical and Electronic Engineering Faculty of Engineering, University Putra Malaysia43400 UPM Serdang, Selangor, Malaysia2012 IEEE International Conference on Power and Energy (PECon), Kota Kinabalu Sabah, Malaysia, 2-5 December 2012.

- 8. "New Cost Effective Cascaded Twenty-One LevelAsymmetrical Inverter with reduced number of switches and DC sources" Nakul Thombre, Ratika Singh Rawat, Priyanka Rana, Umashankar S School of Electrical Engineering VIT University, Vellore Tamilnadu, India.2014

- 9. S. Lai and F.Z. Peng, "Multilevel converters -a new breed of power converters," IEEE Trans. Ind Appl., vol. 32, no. 3, pp. 50917, May/June 1996.

- 10. "Direct Torque Control with Imposed Switching Frequency and Torque Ripple Minimization in an 11-Level Cascaded Inverter" J. Rodriguez', J. Pontt2, S.Kouro3 Electronics Engineering Department, Universidad Technical Federico Santa Maria, Casilla 110-V, Valparaiso, Chile. IEEE 0-7803-7754-0/03/2003.

- 11. Novel Cascaded H-Bridge Multilevel Inverter with Harmonics Elimination" K.Gobinath PG Scholar/Dept. of EEE, S.Mahendran Assistant Prof./Dept. of EEE K.S.Rangasamy College of Technology, Thiruchengode, India, Dr.I.Gnanambal Professor/Dept. of EEE Government College of Engineering, Salem, India. 978-1-4673-2594-3/13/\$31.00 ©2013 IEEE.